Консортиум CXL Consortium опубликовал спецификацию Compute Express Link (CXL) версии 4.0, лучше адаптированную к растущим запросам рабочих процессов в современных центрах обработки данных.

Как заявил Дерек Роде (Derek Rohde), президент CXL Consortium и главный инженер NVIDIA, появление спецификации CXL 4.0 знаменует новый этап в развитии когерентной работы с памятью, обеспечивая удвоение пропускной способности относительно предыдущей версии и вводя дополнительные возможности. Он подчеркнул, что релиз демонстрирует намерение участников консорциума развивать открытые стандарты, стимулирующие инновации и позволяющие всей отрасли масштабироваться под будущие сценарии применения.

Обновлённый стандарт CXL 4.0 поддерживает линии связи с пропускной способностью до 128 ГТ/с, что в два раза выше показателей предшественника, без увеличения задержек. Фактически, стандарт синхронизирован с PCI Express 7.0. Также сохранены улучшения протокола, реализованные в CXL 3.0: FLIT-кадры размером 256 байт, FEC и CRC. Поддерживается полная обратная совместимость со всеми ранними версиями — CXL 3.x, 2.0, 1.1 и 1.0.

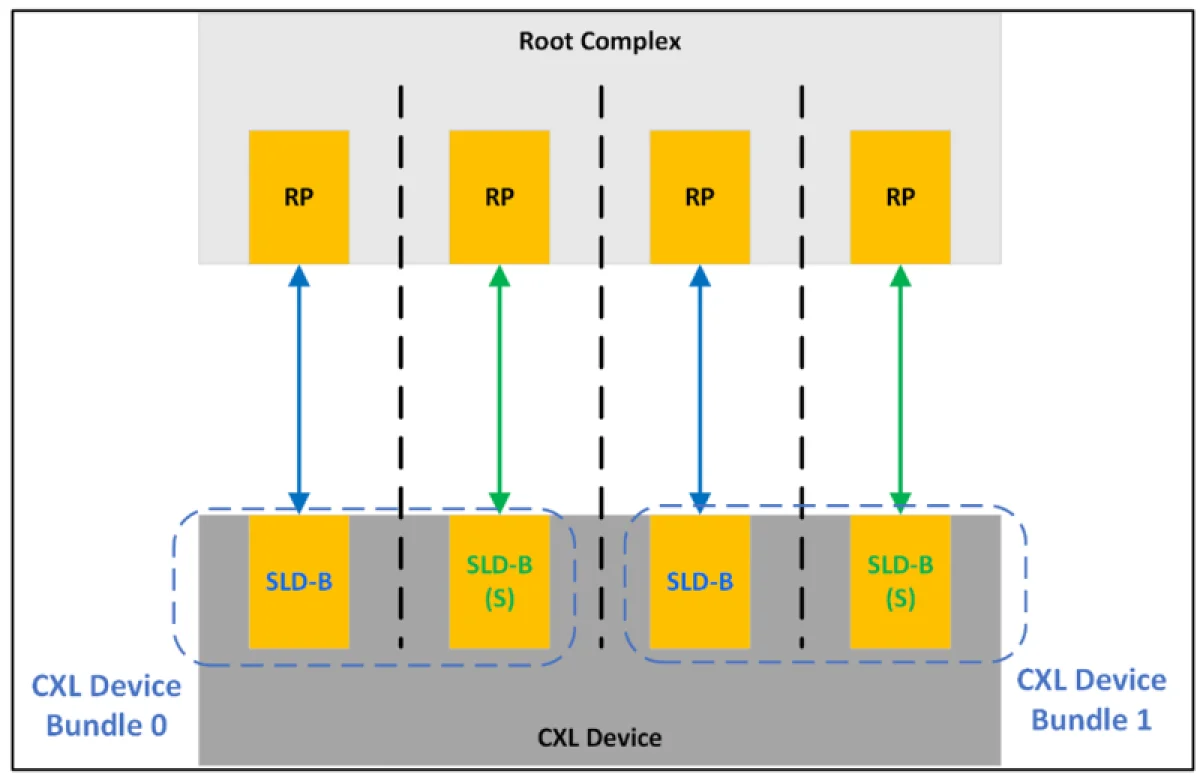

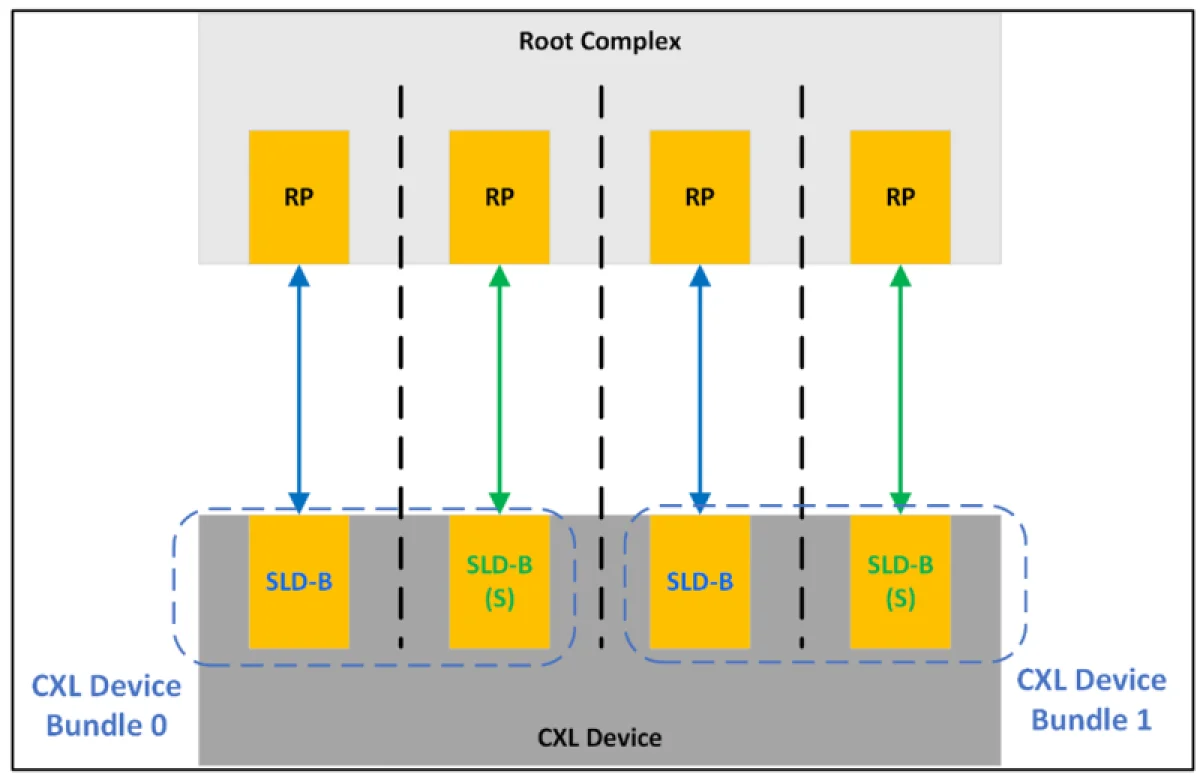

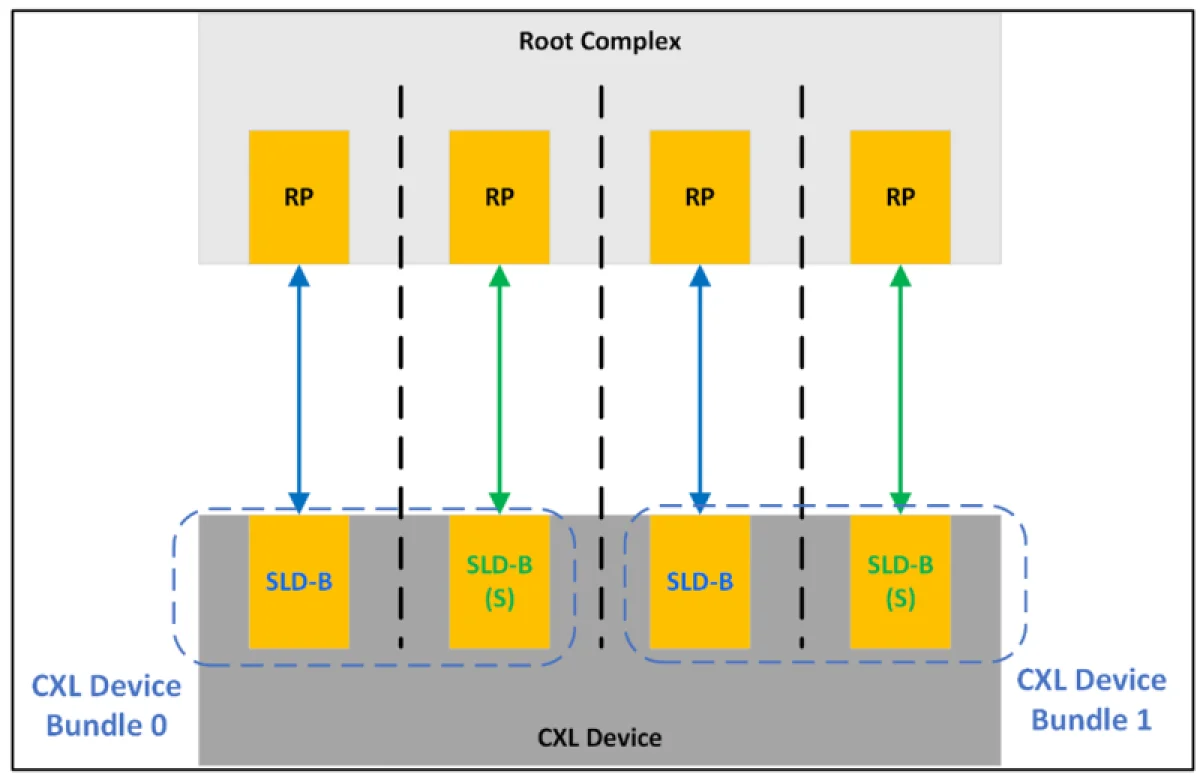

Однако здесь есть особенности. В CXL 4.0 появилась возможность объединения физических портов (Bundled Ports) в единый логический порт, что позволяет устройствам Type 1/2 одновременно подключаться к нескольким корневым портам хоста или коммутатора для повышения пропускной способности. При этом один из физических портов должен быть полнофункциональным, тогда как остальные могут быть оптимизированы только для передачи данных. Агрегированные порты также поддерживают 256-байтный FLIT-режим, но как минимум один физический порт должен работать в 68-байтном режиме для обеспечения обратной совместимости.

Источник изображения: CXL Consortium

Стандарт также предусматривает возможность подключения до четырёх ретрансляторов для расширения зоны передачи данных, улучшения отказоустойчивости (RAS), минимизации вероятных сбоев, а также предоставления более точных и своевременных отчётов о неисправностях. Дополнительно внедрена технология Post Package Repair (PPR), дающая возможность основному устройству запускать диагностику оборудования на этапе загрузки, то есть до начала выполнения операционных задач.

Комментируя релиз CXL 4.0, представители Alibaba отметили, что как соучредитель консорциума CXL компания активно способствует развитию этой экосистемы: «Мы приветствуем появление CXL 4.0 с поддержкой PCIe 7.0 и агрегацией портов, что соответствует растущим потребностям в пропускной способности памяти для современных облачных вычислений. Более того, CXL 4.0 усиливает надёжность и удобство обслуживания систем памяти благодаря усовершенствованным функциям уведомления об ошибках и резервирования памяти. Мы уверены, что CXL 4.0 знаменует новый важный этап в создании модульных, масштабируемых и отказоустойчивых стоечных архитектур для центров обработки данных следующего поколения».

Источник информации: