В последних числах октября компания NextSilicon представила Maverick-2 — интеллектуальный ускоритель вычислений (Intelligent Compute Accelerator, ICA), о котором впервые сообщили годом ранее. Данный процессор уже интегрирован в суперкомпьютер Vanguard-II в Сандийских национальных лабораториях (SNL), относящихся к Министерству энергетики США (DOE), а также применяется несколькими заказчиками. Как пояснил генеральный директор NextSilicon Элад Раз (Elad Raz), организации, работающие в области научных расчётов и высокопроизводительных вычислений (HPC), сталкиваются с ограничениями процессоров и графических ускорителей, вынуждая искать компромиссы, однако архитектура Maverick предлагает решение этой задачи.

Согласно заявлению NextSilicon, современные массовые процессоры «зажаты» в рамках архитектуры фон Неймана, созданной восемь десятилетий назад, где существенная доля ресурсов отводится на вспомогательные функции, такие как предсказание переходов, внеочередное выполнение команд и другие, а не на вычислительные модули. Графические процессоры, в свою очередь, демонстрируют повышенную параллельную производительность, однако для их эффективного применения необходимы специализированные платформы разработки (например, CUDA), управление сложными системами памяти, обеспечение когерентности кэшей и прочие сложности. Специализированные интегральные схемы (ASIC), созданные под определённые задачи искусственного интеллекта, показывают выдающуюся производительность и энергоэффективность, но их проектирование сопряжено с высокими затратами.

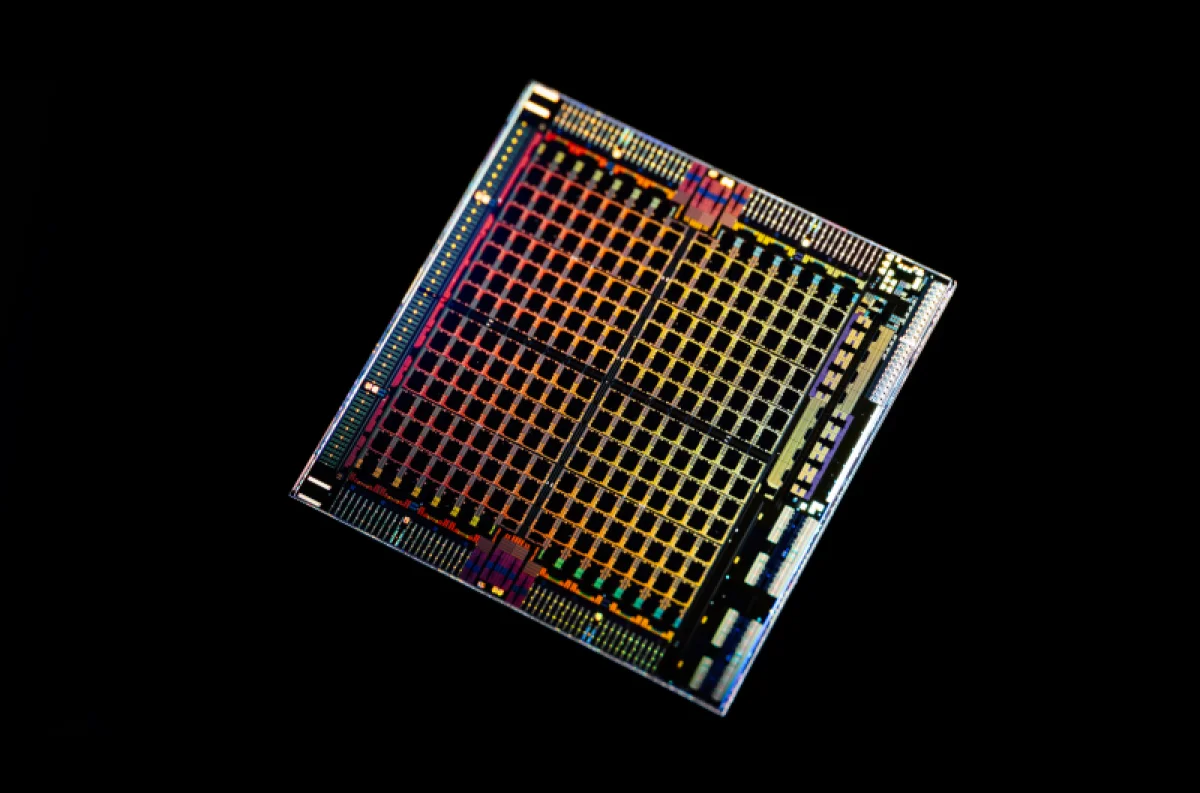

Источник изображения: NextSilicon

NextSilicon предлагает альтернативу в виде чипа, основанного на управлении потоками данных (dataflow), который способен перенастраиваться непосредственно в процессе работы для устранения «узких мест» в коде, не имея при этом ограничений, характерных для CPU и GPU. «В ресурсоёмких приложениях основную часть времени занимает выполнение лишь небольшого фрагмента кода, — отметил Раз. — Нами создан интеллектуальный программный алгоритм, который постоянно анализирует работу приложения. Он точно определяет наиболее часто используемые участки кода и перенастраивает чип для их ускорения. Причём всё это происходит непосредственно во время выполнения программы и занимает наносекунды». ПЛИС (FPGA) также допускают перепрограммирование, однако для этого требуется цикл перезагрузки.

Изображения предоставлены: ServeTheHome/NextSilicon

Основу аппаратной платформы Maverick составляет реконфигурируемая матрица арифметико-логических устройств, занимающая основную площадь кристалла. Её конфигурация может динамически меняться прямо во время выполнения программы. Такой подход обеспечивает повышенную вычислительную производительность за такт (и на единицу энергопотребления) при условии своевременной подачи данных. Специальный алгоритм анализирует исполняемый код, выявляет критические участки и оперативно перестраивает архитектуру чипа. По заявлению NextSilicon, их программно-определяемая архитектура управления потоками данных приближается по эффективности к специализированным ASIC-решениям, сохраняя при этом универсальность и алгоритмическую гибкость.

В архитектуре NextSilicon вычислительные модули (CB) подключены к шине памяти для получения информации, которая временно сохраняется в станциях резервирования (RS). Модуль управления определяет момент активации вычислительных блоков. (RS и модуль управления функционально аналогичны регистровому файлу в традиционных процессорах.) Блоки доступа к памяти (MEP) обрабатывают операции с памятью, формируя запросы к шине и перенаправляя полученные данные в RS. Модуль управления памятью и TLB-кэш отвечают за трансляцию адресов (при необходимости). Остальное пространство CB занимают ALU, которые условно можно рассматривать как эквивалент инструкций. Точное количество вычислительных блоков в чипе не раскрывается, но на фотографии кристалла видно 224 таких модуля.

Компилятор NextSilicon организует из ALU так называемые Mill-ядра в рамках CB, представляющие собой графы взаимосвязанных операций. Поступление данных на вход ALU служит сигналом к выполнению назначенной операции, после чего результат передаётся следующему арифметико-логическому устройству, и так по всей цепочке графа. Уникальной особенностью чипа является возможность автоматического дублирования и оптимального распределения Mill-ядер как внутри одного вычислительного блока, так и между различными CB в процессе работы. При увеличении объёма параллельно обрабатываемых данных создаётся больше Mill-ядер. Однако это относится исключительно к наиболее интенсивно используемым фрагментам кода.

Сооснователь и вице-президент по архитектурным решениям NextSilicon Илан Таяри (Ilan Tayari) подчеркнул ключевое преимущество платформы — способность исполнять произвольный код без дополнительных настроек, независимо от его происхождения: будь то программы для CPU и GPU или алгоритмы искусственного интеллекта. Компилятор NextSilicon, работая с такими языками и платформами, как C++, Fortran, Python, CUDA, ROCm, OneAPI и фреймворками ИИ, разбивает код на сегменты, транслируя их в промежуточный формат для адаптируемого аппаратного обеспечения. «Это выходит за рамки современных решений, — отметил Таяри. — Для специалистов по ИИ такой подход создаёт уникальные перспективы. Ускорение достигается вне зависимости от особенностей модели… будь то нестандартные функции активации, работа с комплексными числами или оригинальные математические методы — всё оптимизируется сразу после установки».

В процессе работы приложения встроенная телеметрия чипа постоянно совершенствует его производительность. К примеру, при активном обмене данными между вычислительными модулями конфигурация графа изменяется для их сближения или перехода, скажем, от векторных операций к матричным. При обнаружении узких мест система автоматически создаёт их дубликаты для распараллеливания задач. Вся оптимизация происходит в реальном времени без участия программиста, что отличает этот метод от, например, VLIW-архитектуры.

Чип Maverick-2 производится по 5-нм технологии TSMC в двух вариантах: монолитном и двухкристальном, с тактовой частотой 1,5 ГГц. Монолитная версия с энергопотреблением 400 Вт предназначена для плат PCIe 5.0 x16, а двухкристальный вариант мощностью 750 Вт рассчитан на OAM-модули. Однокристальная модификация с воздушным охлаждением оснащена 32 управляющими ядрами RISC-V, 96 ГБ памяти HBM3E, кэшем 128 МБ и одним портом 100GbE. Двухкристальная OAM-версия с жидкостным охлаждением включает 64 управляющих ядра RISC-V, 192 ГБ HBM3E, кэш-память 256 МБ и два интерфейса 100GbE.

Важно подчеркнуть, что приведённые показатели TDP являются пиковыми, и, согласно данным ServeTheHome, в большинстве сценариев энергопотребление окажется ниже. NextSilicon сообщает о достижении 600 Гфлопс при 750 Вт в тесте HPCG (что вдвое экономичнее аналогов), а для UBB — 4,8 Тфлопс при 6 кВт. Были протестированы одно- и двухкристальные конфигурации Maverick2. В STREAM чип продемонстрировал 5,2 Тбайт/с пропускной способности, а в GUPS — 32,6 GUPS при 460 Вт, опередив ЦПУ в 22 раза и графические ускорители почти в 6 раз в таких задачах, как СУБД, онлайн-принятие решений ИИ-агентами и инференс на фрагментированных данных.

В испытании Google PageRank (PR) чип обработал 40 млрд страниц/с, что десятикратно превышает результаты топовых GPU при половинном энергопотреблении. Компания акцентировала, что при работе с крупными графами (свыше 25 Гбайт) лидирующие GPU не завершили тест, тогда как Maverick-2 справился, подтвердив необходимость гибких архитектур для сложных вычислений в современных ИИ-системах, социальной аналитике и сетевой аналитике.

«Эти показатели получены на стандартном, неизменённом коде приложений», — отметил Эяль Нагар (Eyal Nagar), сооснователь и вице-президент по R&D NextSilicon. «Наши конкуренты вынуждены привлекать специалистов для адаптации кода, BIOS, прошивок, ОС и настроек для достижения заявленных результатов. NextSilicon же обеспечивает выдающуюся производительность на готовом программном обеспечении», — добавил он.

Компания NextSilicon также продемонстрировала тестовый образец процессора корпоративного класса, основанного на архитектуре RISC-V, который станет центральным элементом в новом поколении ускорителей Maverick-3. Процессор Arbel, спроектированный с нуля с 10-командным конвейером, представляет собой развитие более компактных ядер RISC-V из платформы Maverick-2, предназначенных для обработки последовательных инструкций. Как утверждает производитель, эти ядра демонстрируют производительность, сопоставимую с решениями AMD Zen 5 и Intel Lion Cove.

Согласно заявлению NextSilicon, революционная производительность Arbel обеспечивается четырьмя фундаментальными архитектурными усовершенствованиями:

- Масштабный конвейер обработки команд с пропускной способностью 10 инструкций и буфером переупорядочения на 480 операций, позволяющий процессору эффективно распределять вычислительные ресурсы.

- Тактовая частота 2,5 ГГц гарантирует высокую однопоточную производительность при оптимальном энергопотреблении.

- Мощный исполнительный блок с поддержкой параллельного выполнения 16 скалярных операций и четырьмя 128-бит векторными модулями для эффективной работы с параллельными вычислениями.

- Продвинутая система кэширования с 64 КБ L1, 1 МБ L2 и масштабируемым кэшем L3 (2 МБ на ядро) обеспечивает минимальные задержки доступа к данным и исключает узкие места в работе с памятью.

- Современный алгоритм предсказания переходов TAGE значительно повышает точность прогнозирования и снижает количество ошибочных операций.

«Это реальный кремниевый кристалл, произведённый по 5-нм технологии TSMC — полностью оригинальная разработка, не основанная на лицензированных решениях. Наши инженеры создали его для реализации перспективных идей NextSilicon», — подчеркнул Элад Раз.

По данным компании, флагманский ускоритель Maverick2, помимо SNL, уже используется «десятками» заказчиков. Его массовые поставки начнутся в начале 2026 года, чтобы обеспечить значительный портфель заказов. NextSilicon сотрудничает с различными организациями, от Министерства энергетики США до ведущих научно-исследовательских институтов, а также коммерческих клиентов в сфере финансовых услуг, энергетики, производства и биологических наук. Программы раннего внедрения для новых клиентов уже доступны через партнёров Penguin Solutions и Dell Technologies.

Ускоритель следующего поколения NextSilicon Maverick3 будет поддерживать вычисления с пониженной точностью для ИИ-задач и, как ожидается, появится в продаже в 2027 году, пишет EE Times.

Источники:

- NextSilicon

- EE Times

- ServeTheHome